- EIM 單bit 錯誤注入驗證

/*** @page misra_violations MISRA-C:2012 violations** @section [global]* Violates MISRA 2012 Advisory Rule 8.7, External variable could be made static.* The external variables will be used in other source files in application code.**//* Channel configurations */const eim_user_channel_config_t eim_InitConfig0[EIM_CHANNEL_COUNT0] ={/* Channel configuration 0 */{.channel = 0U,.checkBitMask = 0U,.dataMask = 1U,.enable = true}};

erm config:

/* Interrupt configurations *//* Interrupt configuration 0 */const erm_interrupt_config_t erm_Interrupt0 ={.enableSingleCorrection = true,.enableNonCorrectable = true};/* ERM configurations *//* ERM configuration 0 */const erm_user_config_t erm_InitConfig0[ERM_CHANNEL_COUNT0] ={/* Channel configuration 0 */{.channel = 0U,.interruptCfg = &erm_Interrupt0}};

測試程式碼:

#include <stdio.h>

#include <rtthread.h>

#include <rtdevice.h>

#include <board.h>

int eim_correct(void)

{

uint32_t test;

uint32_t addr;

erm_ecc_event_t retValue = ERM_EVENT_NONE;

/* Initialize address used to test */

*(uint32_t *)0x1FFFFFF0U = 0U;

/* Hardware initialization */

/* Initial for ERM module */

ERM_DRV_Init(INST_ERM_CONFIG_1, ERM_CHANNEL_COUNT0, erm_InitConfig0);

/* Initial for EIM module */

EIM_DRV_Init(INST_EIM_CONFIG_1, EIM_CHANNEL_COUNT0, eim_InitConfig0);

/* Read any address on RAM */

/* Enable read region Ram (0x1FFF8000 - 0x20006FFF) when debug equal Flash */

test = *(uint32_t *)0x1FFFFFF0U;

(void)test;

/* Deinit EIM module */

EIM_DRV_Deinit(INST_EIM_CONFIG_1);

/* Check error and get address which EIM injection error */

retValue = ERM_DRV_GetErrorDetail(INST_ERM_CONFIG_1, 0U, &addr);

rt_kprintf("erm status %s error addr is 0x%08x\n",\

retValue == ERM_EVENT_NONE ? "ERM_EVENT_NONE" :\

(retValue == ERM_EVENT_SINGLE_BIT ? "ERM_EVENT_SINGLE_BIT" :\

(retValue == ERM_EVENT_NON_CORRECTABLE ? "ERM_EVENT_NON_CORRECTABLE" : "ERM_EVENT_NONE")),\

addr);

return 0;

}

MSH_CMD_EXPORT_ALIAS(eim_correct, eim1 ,eim correct test);

執行上述測試程式碼,輸入eim1 測試指令,ERM 模組已經按照預期的偵測到 Single bit 錯誤。

- ERM 單bit 錯誤中斷驗證

在上述程式碼的基礎上追加ERM 中斷啟用,查看中斷函數能否被正常執行,對應程式碼修改如下:

- EIM 多bit 錯誤注入驗證

const eim_user_channel_config_t eim_InitConfig1[EIM_CHANNEL_COUNT1] ={/* Channel configuration 0 */{.channel = 0U,.checkBitMask = 3U,.dataMask = 0U,.enable = true}};

新增如下測試指令eim2:

/*!

\brief The ERM_ISR funcion invert state Led

*- Clear event when have notify interrupt

*/

void erm_doublebit_isr(void)

{

uint32_t addr;

erm_ecc_event_t retValue = ERM_EVENT_NONE;

/* Deinit EIM module */

EIM_DRV_Deinit(INST_EIM_CONFIG_1);

/* Check error and get address which EIM injection error */

retValue = ERM_DRV_GetErrorDetail(INST_ERM_CONFIG_1, 0U, &addr);

rt_kprintf("erm isr status %s error addr is 0x%08x\n",\

retValue == ERM_EVENT_NONE ? "ERM_EVENT_NONE" :\

(retValue == ERM_EVENT_SINGLE_BIT ? "ERM_EVENT_SINGLE_BIT" :\

(retValue == ERM_EVENT_NON_CORRECTABLE ? "ERM_EVENT_NON_CORRECTABLE" : "ERM_EVENT_NONE")),\

addr);

/* The interrupt notification will be cleared.*/

ERM_DRV_ClearEvent(INST_ERM_CONFIG_1, 0U, ERM_EVENT_NON_CORRECTABLE);

}

int eim_double_bit(void)

{

uint32_t test;

uint32_t addr;

erm_ecc_event_t retValue = ERM_EVENT_NONE;

/* Initialize address used to test */

*(uint32_t *)0x1FFFFFF0U = 0U;

/* Install IRQ Handlers for ERM and SysTick */

INT_SYS_InstallHandler(ERM_double_fault_IRQn, erm_doublebit_isr, (isr_t *)0);

/* Enable ERM IRQ */

INT_SYS_EnableIRQ(ERM_double_fault_IRQn);

/* Hardware initialization */

/* Initial for ERM module */

ERM_DRV_Init(INST_ERM_CONFIG_1, ERM_CHANNEL_COUNT0, erm_InitConfig0);

/* Initial for EIM module */

EIM_DRV_Init(INST_EIM_CONFIG_1, EIM_CHANNEL_COUNT1, eim_InitConfig1);

/* Read any address on RAM */

/* Enable read region Ram (0x1FFF8000 - 0x20006FFF) when debug equal Flash */

test = *(uint32_t *)0x1FFFFFF0U;

(void)test;

/* Deinit EIM module */

EIM_DRV_Deinit(INST_EIM_CONFIG_1);

/* Check error and get address which EIM injection error */

retValue = ERM_DRV_GetErrorDetail(INST_ERM_CONFIG_1, 0U, &addr);

rt_kprintf("erm status %s error addr is 0x%08x\n",\

retValue == ERM_EVENT_NONE ? "ERM_EVENT_NONE" :\

(retValue == ERM_EVENT_SINGLE_BIT ? "ERM_EVENT_SINGLE_BIT" :\

(retValue == ERM_EVENT_NON_CORRECTABLE ? "ERM_EVENT_NON_CORRECTABLE" : "ERM_EVENT_NONE")),\

addr);

return 0;

}

MSH_CMD_EXPORT_ALIAS(eim_double_bit, eim2 ,eim uncorrect test);

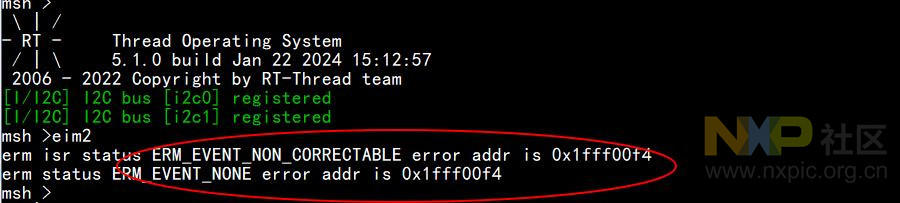

輸入eim2 指令驗證:

從上面的log 可知,已經按照預期的觸發了不可糾正ECC錯誤,對應的地址和上面的 單bit異常 的地址是相同的原因 是中斷向量表的地址相同。

沒有留言:

張貼留言